About Me

I am Yi-Cheng Lo (羅儀誠), or Eason. I am currently a fourth-year undergraduate student majoring in Electrophysics at National Yang Ming Chiao Tung University (NYCU).

Currently, I am an undergraduate researcher in the Exploratory Device Compute Laboratory (ECDL) under the supervision of Prof. Tsung-En Lee. My work focuses on the intersection of computational modeling and experimental characterization of next-generation semiconductor devices.

Research Interests

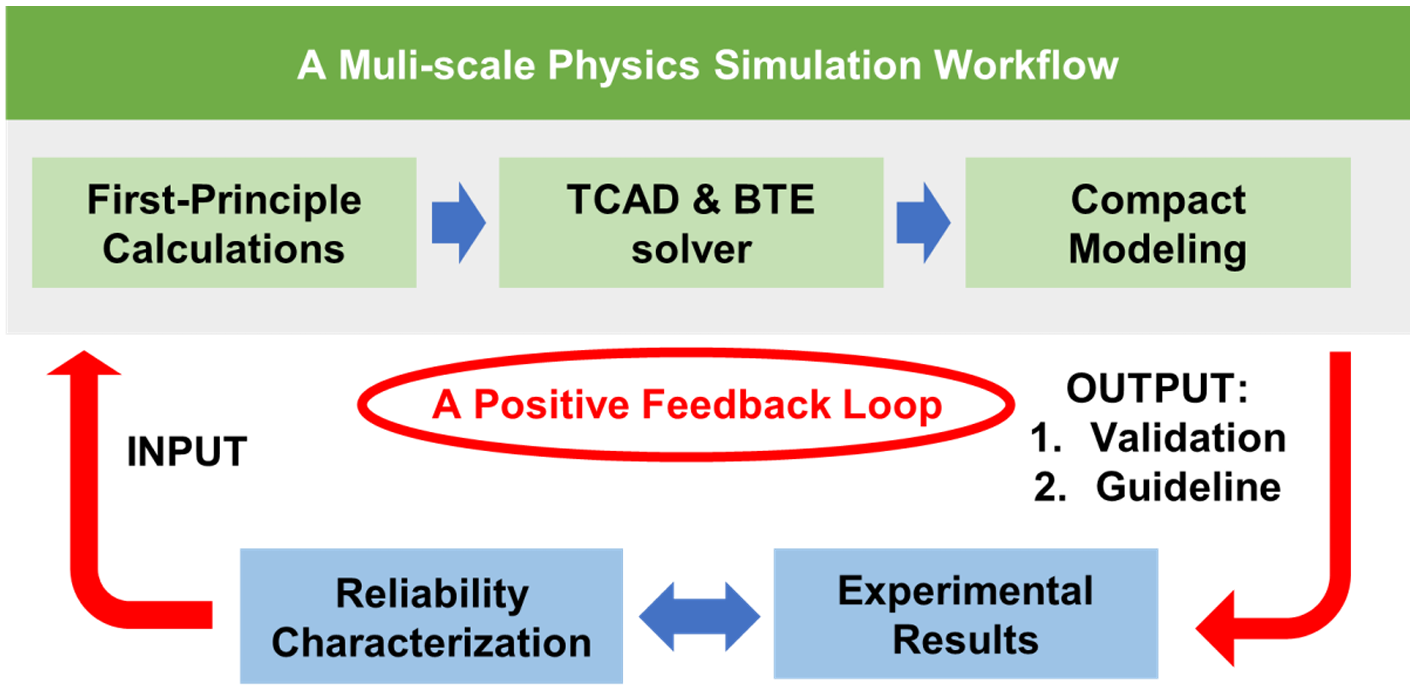

1. Multi-scale Simulation and Modeling of 2D Materials

I am interested in developing a holistic understanding of carrier transport in 2D materials (such as WSe2 and MoS2) by bridging the gap between atomic-level physics and macro-scale device performance:

- Atomic Scale: Utilizing First-Principles calculations—Density Functional Theory (DFT) and Non-Equilibrium Green’s Function (NEGF)—to investigate electronic band structures and contact physics.

- Device Scale: Implementing subband Boltzmann Transport Equations (BTE) via Monte Carlo (MC) methods and Drift-Diffusion (DD) models to evaluate device-level characteristics and scaling limits.

2. Advanced Reliability Characterization

My research aims to uncover the degradation mechanisms inherent in 2D field-effect transistors (FETs), particularly focusing on the interface between the gate stack and the Van der Waals (vdW) gap:

- Measurement Techniques: Employing characterization methods ranging from ultra-fast pulses to long-term stress durations to study Bias Temperature Instability (BTI), Hysteresis, etc.

- Physical Modeling: Combining the Non-Radiative Multi-Phonon (NMP) model with device level modeling to describe charge trapping/detrapping kinetics, providing insights for fabrication process optimization and device lifetime prediction.